# DAG 7.1S Card User Guide EDM01-17

www.endace.com

Published by:

Endace Limited

Building 7

Lambie Drive

PO Box 76802 Manukau City 1702 New Zealand

Phone: +64 9 262 7260

Fax: +64 9 262 7261

support@endace.com

www.endace.com

#### **International Locations**

New Zealand Endace Technology® Ltd

Level 9 85 Alexandra Street

PO Box 19246 Hamilton 2001 New Zealand

Phone: +64 7 839 0540 Fax: +64 7 839 0543 Americas Endace USA® Ltd

Suite 220 11495 Sunset Hill Road

Reston Virginia 20190 United States of America

Phone: ++1 703 382 0155 Fax: ++1 703 382 0155 **Europe, Middle East & Africa** Endace Europe® Ltd

Sheraton House Castle Park

Cambridge CB3 0AX United Kingdom

Phone: ++44 1223 370 176 Fax: ++44 1223 370 040

**Copyright 2005-2006**<sup>©</sup> **Endace Limited. All rights reserved.** No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher.

#### **Protection Against Harmful Interference**

When present on equipment this manual pertains to, the statement "This device complies with part 15 of the FCC rules" specifies the equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to Part 15 of the Federal Communications Commission [FCC] Rules.

These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment.

This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications.

Operation of this equipment in a residential area is likely to cause harmful interference in which case the user will be required to correct the interference at his own expense.

#### **Extra Components and Materials**

The product that this manual pertains to may include extra components and materials that are not essential to its basic operation, but are necessary to ensure compliance to the product standards required by the United States Federal Communications Commission, and the European EMC Directive. Modification or removal of these components and/or materials, is liable to cause non compliance to these standards, and in doing so invalidate the user's right to operate this equipment in a Class A industrial environment.

#### Disclaimer

Whilst every effort has been made to ensure accuracy, neither Endace Limited nor any employee of the company, shall be liable on any ground whatsoever to any party in respect of decisions or actions they may make as a result of using this information.

Endace Limited has taken great effort to verify the accuracy of this manual, but assumes no responsibility for any technical inaccuracies or typographical errors.

In accordance with the Endace Limited policy of continuing development, design and specifications are subject to change without notice.

# **Table of Contents**

| Chapter 1: Introduction                   | 1        |

|-------------------------------------------|----------|

| Overview                                  | 1        |

| Purpose of this User Guide                | 1        |

| System Requirements                       | 23       |

| Card Description                          |          |

| Card Architecture                         | 4        |

| Extended Functions                        | 5        |

| Chapter 2: Installation                   | 7        |

| Introduction                              | 7        |

| DAG Driver Device                         | 7        |

| Inserting the DAG Card                    | 7        |

| Port Connectors                           | 8        |

| Pluggable Optical Transceivers            | 8        |

| Chapter 3: Configuring the Card           | 11       |

| Introduction                              | 11       |

| Line Characteristics                      | 11       |

| LEDs and Inputs                           | 12       |

| Receiver Port Signal Levels               | 12       |

| Specific Network Configuration            | 13       |

| Chapter 4: Concatenated Configuration     | 15       |

| Load the FPGA Images                      | 15       |

| Available Configurations                  | 15       |

| Display Current Configuration             | 15       |

| Verify Optical Signal                     | 17       |

| Verify Mapping/ Framing Setup             | 18       |

| ATM Mode                                  | 19       |

| PoS Mode                                  | 20       |

| Interface Statistics                      | 21       |

| Status Conditions<br>Varify Configuration | 23<br>24 |

| Verify Configuration                      | 24       |

| Chapter 5: Channelised Configuration      | 25       |

| Load the FPGA Images                      | 25       |

| Available Configurations                  | 25       |

| Display Current Configuration             | 25       |

| Verify Optical Signal                     | 27       |

| Verify Mapping/ Framing Setup             | 28       |

| Configure Line Type                       | 29       |

| Interface Statistics<br>E1 OC-12          | 30       |

| T1 OC-12                                  | 30       |

| Interface Statistics (cont.               | 31<br>32 |

| Status Conditions                         | 32       |

| Verify Configuration                      | 33       |

| Configuring Channels                      | 34       |

| Valid Configurations                      | 34       |

| Supported Channel Types                   | 36       |

| Configuration File                        | 36       |

|                                           |          |

i

#### **Chapter 6: Capturing Data**

| Chapter 6: Capturing Data                      | 39       |

|------------------------------------------------|----------|

| Starting a Session                             | 39       |

| Setting Captured Packet Size                   | 39       |

| Snaplength                                     | 39       |

| Variable/Fixed Length                          | 40       |

| Enabling/ Disabling Ports                      | 40       |

| High Load Performance                          | 41       |

| Overview                                       | 41       |

| Avoiding Packet Loss                           | 41       |

| Detecting Packet Losses                        | 41       |

| Increasing Buffer Size                         | 42       |

| Transmitting                                   | 42       |

| Configuration                                  | 42       |

| Explicit Packet Transmission                   | 43       |

| Trace Files<br>Configuring Extended Europtions | 43<br>44 |

| Configuring Extended Functions<br>Overview     | 44 44    |

| Loading the Images                             | 44 44    |

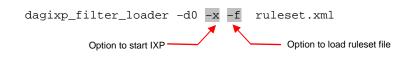

| Starting the IXP                               | 44 45    |

| Directing Data to the IXP                      | 45       |

| Using the AAL Reassembler                      | 45       |

| Using the PoS IP Filter                        | 46       |

| 6                                              | -        |

| Chapter 7: Synchronizing Clock Time            | 47       |

| Overview                                       | 47       |

| DUCK Configuration                             | 47       |

| Common Synchronization                         | 47       |

| Timestamps                                     | 48       |

| Configuration Tools                            | 49       |

| Card with Reference                            | 50       |

| Overview                                       | 50       |

| Pulse Signal from External Source              | 50       |

| Connecting the Time Distribution Server        | 50       |

| Testing the Signal                             | 50       |

| Single Card No Reference                       | 51       |

| Two Cards No Reference                         | 51       |

| Synchronising with Each Other                  | 52<br>52 |

| Synchronising with Host<br>Connector Pin-outs  | 53       |

| Connector 1 m-outs                             | 55       |

| Chapter 8: Data Formats                        | 55       |

| Overview                                       | 55       |

| Generic Header                                 | 55       |

| Type-1 Record                                  | 57       |

| Type-3 Record                                  | 57       |

| Type-4 Record                                  | 57       |

| Type-5 Record                                  | 58       |

| Type-7 Record                                  | 59       |

| Type 9 Record                                  | 60       |

| Type 12 Record                                 | 61       |

| Type 18 Record                                 | 62       |

| Chapter 9 Troubleshooting                      | 63       |

| Reporting Problems                             | 63       |

|                                                |          |

# Chapter 1: Introduction

| Overview                         | The Endace DAG 7.1S card provides the means to transfer data at the full speed of the network into the memory of the host PC, with zero packet loss guaranteed in even worst-case conditions. Further, unlike a NIC, Endace products actively manage the movement of network data into memory without consuming any of the host PC's resources. The full attention of the CPU remains focused on the analysis of incoming data without a constant stream of interruptions as new packets arrive from the network. For a busy network link, this feature has a turbo-charging effect similar to that of adding a second CPU to the system. |  |  |  |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                  | to provide high efficiency monitoring and transmission of ATM, POS or Bit<br>HDLC traffic with precision timestamping capability.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                                  | It supports the following:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                                  | • Concatenated POS/ATM receive and transmit over 4 x OC-3c/STM-1c or 4 x OC-12c/STM-4c.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                                  | • Channelised Bit HDLC/ATM receive and transmit over 4 x OC-3/STM-1 or 2 x OC-12/STM-4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| Purpose of<br>this User<br>Guide | <b>Description</b><br>The purpose of this User Guide is to provide you with an understanding of<br>the DAG card architecture and functionality and to guide you through the<br>following:                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                                  | • Installing the card and associated software and firmware,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                                  | • Configuring the card for your specific network requirements,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                  | Running a data capture session,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|                                  | • Synchronising clock time,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                                  | Data formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                                  | You can also find additional information relating to functions and features of the DAG 7.1S card in the following documents which are available from the Support section of the Endace website at <u>www.endace.com</u> :                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                                  | • EDM04-08 Configuration and Status API Programming Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                                  | EDM04-13 SAR API Programming Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                                  | • EDM04-11 IXP Filter API Programming Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                                  | • EDM04-08 DAG IXP Filter Loader User Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                                  | This User Guide and the Linux and Window Guides are also available in PDF format on the Installation CD shipped with your DAG 7.1S card.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

1

System

#### General

**Requirements** The minimum system requirements for the DAG 7.1S card are :

- PC, at least Intel Xeon 1.8GHz or faster

- Minimum of 256 MB RAM

- At least one free PCI-Express slot supporting at least one lane

- Software distribution requires 30MB free space

- 6GB for installation of Endace software, which is optional

### **Operating System**

This User Guide assumes you are installing the DAG card in a PC which already has an operating system installed.

However for convenience, a copy of Debian Linux 3.1 (Sarge) is provided as a bootable ISO image on the CDs that is shipped with the DAG card.

To install either the Linux/FreeBSD or Windows operating system please refer to the following documents which are also included on the CD that is shipped with the DAG card.

- EDM04-01 Linux FreeBSD Software Installation Guide

- EDM 04-02 Windows Software Installation Guide

#### **Other Systems**

For advice on using an operating system that is substantially different from either of those specified above, please contact Endace Customer Support at <a href="mailto:support@endace.com">support@endace.com</a>

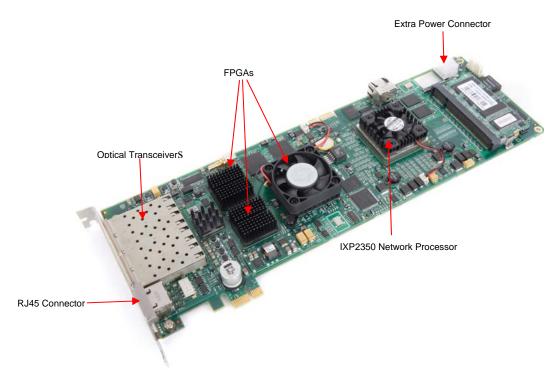

# Card Description

The DAG 7.1S SDH/SONET Network Monitoring Card provides either four STM-1 (OC3) or two STM-2 (OC12) interfaces supporting concatenated or channelised ATM or Packet Over Sonet (POS) networks.

The DAG 7.1S has four optical transceivers which can be operated simultaneously.

The key features of the card are:

- Four interfaces allow full line rate capture and processing for 4 x STM-1/OC-3 or 2 x STM-2/OC-12.

- Fully programmable Intel IXP Network Processor

- PCI Express bus interface.

- 1244Mpps raw transmit and receive bandwidth.

- Combined FPGA and network processor architecture.

- Channelised and concatenated support.

- ATM AAL2 and AAL5 segmentation and reassembly.

- PoS IP filtering

# Card Architecture

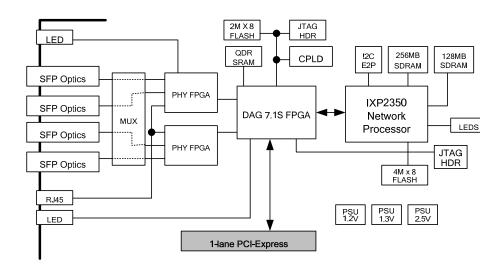

Serial SONET/SDH optical data is received by four optical interfaces, and passed through deserializers.

The network data feeds immediately into two physical layer FPGAs. The SONET/SDH payload data is then sent to the main FPGA.

The FPGA contains the packet record processor, PCI Express interface logic and the DAG Universal Clock Kit (DUCK) timestamp engine. The DUCK provides high resolution per packet timestamps which can be accurately synchronised..

**Note:** For further information on the DUCK and time synchronising please refer to <u>*Chapter 7: Synchronising Clock Time*</u> later in this User Guide.

An Intel IXP network processor is logically located next to the main FPGA. The main FPGA can route packets to either the IXP network processor for additional processing before routing onto the host or directly to the host via the PCI-Express port.

The following diagram shows the card's major components and the flow of data.

# Extended Functions

In addition to standard packet capture the DAG 7.1S card also provides TCP/IP Filtering and Classification and ATM Segmentation and Reassembly

# **TCP/IP Filtering and Classification**

This feature allows you to classify packets into arbitrary categories which then drop, retransmit or capture a packet to the host based upon the result. You can also change filter rules "on the fly" with any loss of data

The specifications for the IP filtering/packet classification are:

- Packets are classified and filtered by IP header (both IPv4 and IPv6) and/or UDP/TCP/SCTP port number.

- Up to 1024 IP header classification rules.

- Up 254 UDP/TCP/SCTP port or ICMP type rules can set per IP header classification.

- Classification rules are assigned a user-defined 14-bit identifier

- Packets matching classification rules are assigned the matching rule's identifier.

- Programmable actions may be associated with each rule identifier. For example the packet should either be dropped, or presented to the host.

- Packets presented to the host include the rule-match identifier in the record header.

### AAL2/AAL5 Reassembly

This feature allows you to eliminate the significant CPU load associated with AAL2/AAL5 reassembly on a busy ATM link by offloading this process to the DAG card. It also provides the ability to reduce volume of captured data to only what is required by filtering on VPI/VCI pairs.

The Reassembler specifications are:

- Supports up to 8160 simultaneously active VCI/VPI/CIDs

- Supports simultaneous reassembly of AAL2 and AAL5 frames up to 8kB long.

- VPI/VCI scanning

- Supports up to full STM-4/OC-12 cell rate on two interfaces simultaneously (approx 2.8 million cells/sec), or four full STM-1/OC-3 interfaces for AAL 5 reassembly.

- Supports 2 x STM-1/OC-3 cell rate on combined four interfaces (approx 0.8 million cells/sec) for AAL2 reassembly.

- Optional ATM cell filtering prior to reassembly.

EDM 01-17 DAG 7.1S Card User Guide

# Chapter 2: Installation

| Introduction              | A DAG 7.1S card can be installed in any free PCI-Express slot.                                                                                                                                                                                                     |  |  |  |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                           | The DAG 7.1S card operates on a single lane PCI-Express, this interface is capable of providing a maximum throughput of 1.8Gbits/s for both receive and transmit.                                                                                                  |  |  |  |

|                           | You can run multiple DAG 7.1S cards on one bus. By default, the DAG driver supports up to four DAG cards in one system.                                                                                                                                            |  |  |  |

| DAG Driver<br>Device      | The DAG device driver must be installed before you install the DAG card itself.                                                                                                                                                                                    |  |  |  |

|                           | If you have not already completed this please follow the instructions in <i>EDM04-01 Linux FreeBSD Software Installation Guide</i> or <i>EDM 04-02 Windows Software Installation Guide</i> as appropriate, which are included on the CD shipped with the DAG card. |  |  |  |

| Incorting the             | To insert the DAG card in the PC follow the steps described below:                                                                                                                                                                                                 |  |  |  |

| Inserting the<br>DAG Card | -                                                                                                                                                                                                                                                                  |  |  |  |

| DAG Caru                  | <ul><li>Turn power to the computer OFF,</li><li>Remove the PCI bus slot screw and cover,</li></ul>                                                                                                                                                                 |  |  |  |

|                           | <ul> <li>Remove the PCI bus slot screw and cover,</li> <li>Insert DAG card into PCI-e bus slot ensuring that it is firmly seated in</li> </ul>                                                                                                                     |  |  |  |

|                           | the slot,                                                                                                                                                                                                                                                          |  |  |  |

|                           | • Check the free end of the card fits securely into the card-end bracket that supports the weight of the card,                                                                                                                                                     |  |  |  |

|                           | • Secure the card with the bus slot screw,                                                                                                                                                                                                                         |  |  |  |

|                           | • Connect the extra power connector located on the top edge of the card.                                                                                                                                                                                           |  |  |  |

|                           | <ul> <li>Note: Ensure you do this before powering up the computer. Failure</li> <li>to do so may cause damage to the card.</li> </ul>                                                                                                                              |  |  |  |

|                           | Extra Power<br>Connector                                                                                                                                                                                                                                           |  |  |  |

• Turn power to the computer ON.

# Port Connectors

The DAG 7.1S has 4 SFP socket connectors. Each connector consists of an optical fibre transmitter and receiver.

The upper connector of each pair is used for the transmit signal. These can be connected to daisy-chain systems if you have facility loopback (fcl) set on the card. You can also connect them if you are using a data generation programme.

The bottom connector of each pair is used for the received signal.

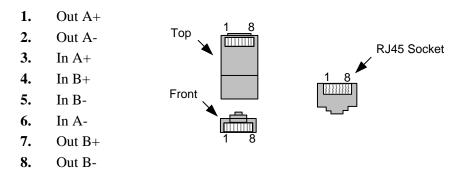

There is an 8-pin RJ-45 socket located below the optical port connectors on the car bracket. This is available for connection to an external time synchronisation source.

Pluggable Optical Transceivers

#### Overview

The DAG7.1S card uses industry standard Small Form-factor Pluggable (SFP) optical transceivers.

The transceivers consists of two parts:

- Mechanical chassis attached to the circuit board

- Transceiver unit which may be inserted into the chassis

**Note:** You must select the correct transceiver type to match the optical parameters of the network to which you want t connect. Configuring the card with the wrong transceiver type may damage the card.

You can connect the transceiver to the network via LC-style optical connectors.

For further information on Pluggable Optical Transceiver please refer to the Endace website at <u>www.endace.com/dagpluggable.htm</u>.

#### **Setting Power**

The optical power range depends on the particular SFP module that is fitted to the DAG card.

However Endace recommends the SFP modules described below which can be supplied with the DAG 7.1S card:

| Manufacturer                   | Part number  |

|--------------------------------|--------------|

| Finisar                        | FTRJ1322     |

| Finisar                        | FTRJ1323     |

| Optical Communication Products | TRPD12MM3EAS |

| Optical Communication Products | TRPD03MM3EAS |

# Pluggable Optical Transceivers (cont.)

Optical power is measured in dBm. This is decibels relative to 1 mW where 10 dB is equivalent to a factor of 10 in power.

The optical power is always a negative value, indicating power that is less than 1 mW. The most sensitive devices can work at power levels down as low as -30dBm or 1 $\mu$ W.

The DAG 7.1S card optical power module configuration for Multi Mode Fibre (MMF) and Single Mode Fibre (SMF) is shown below:

| Part #       | Fibre | Data<br>Rate | Max<br>Pwr | Min<br>Pwr | Nom<br>Pwr | Mode              |

|--------------|-------|--------------|------------|------------|------------|-------------------|

| FTRJ1322     | SMF   | 622          | -8dBm      | -28dBm     | -          | OC-12 Single Mode |

| FTRJ1323     | SMF   | 155          | -8dBm      | -28dBm     | -          | OC-3 Single Mode  |

| TRPD12MM3EAS | MMF   | 622          | -          | -          | -          | OC-12 Multi Mode  |

| TRPD03MM3EAS | MMF   | 155          | -          | -          | -          | OC-3 Multi Mode   |

### **Power Input**

**Note**: The optical power input to the DAG card must be within the receiver's dynamic range of 0 to -22dBm. If it is slightly outside of this range it will cause an increased bit error rate. If it is significantly outside of this range the system will not be able to lock onto the SONET signal.

When power is above the upper limit the optical receiver saturates and fails to function. When power is below the lower limit the bit error rate increases until the device is unable to obtain lock and fails. In extreme cases, excess power can damage the receiver.

When you set up the DAG card you should measure the optical power at the receiver and ensure that it is within the specified power range. If it is not, adjust the input power as follows:

- Insert an optical attenuator if power is too high, or

- Change the splitter ratio if power is too high or too low.

### **Splitter Losses**

Splitters have the insertion losses either marked on their packaging or described in their accompanying documentation. General guidelines are:

- A 50:50 splitter will have an insertion loss of between 3 dB and 4 dB on each output

- 90:10 splitter will have losses of about 10 dB in the high loss output, and <2 dB in the low loss output

**Note:** A <u>single mode fibre</u> connected to a multi-mode input will have minimal extra loss. However a <u>multi-mode fibre</u> connected to a single mode input will create large and unpredictable loss.

EDM 01-17 DAG 7.1S Card User Guide

# Chapter 3: Configuring the Card

Introduction

Configuring the DAG card for data capture involves the following steps:

- Loading the images and programming the FPGAs,

- Setting the link,

- Checking the link,

- Configuring the connections,

- Capturing data.

The DAG 7.1S card uses four integrated SONET/SDH ATM/PoS physical layer interface devices to support capture of ATM cells or Bit HDLC and PoS data frames.

The dagconfig tool which is also supplied with the DAG card allows you to configure the card to your specific network requirements as well as view interface statistics. Sample dagconfig outputs are shown later in this chapter.

# Line Characteristics

#### Overview

**Characteristics** It is important that you understand the physical characteristics of the network to which you want to connect before you begin configuring the card.

Because of its flexibility the card will accept a wide range of settings. However if they are not the correct settings for your network, the card will not function as expected.

**Note:** If you are unsure about which of the options listed below apply to your network, please contact your Network Administrator for further information before proceeding with configuring the card.

### Supported Line Types

The line characteristics supported by the DAG 7.1S card are described below.

| PoS/ATM      | Packet over SONET/Asynchronous Transfer Mode.                                                                  |

|--------------|----------------------------------------------------------------------------------------------------------------|

| OC-3/OC-3c   | A SONET network line with transmission speeds up to 155.52 Mbit/s using fiber optics. Also called STM-1 (SDH). |

| OC-12/OC-12c | A SONET network line with transmission speeds up to 622.08 Mbit/s using fiber optics. Also called STM-4 (SDH). |

| STM-1/STM-1c | An SDH line equivalent to OC-3 (SONET).                                                                        |

| STM-4/STM-4c | An SDH line equivalent to OC-12 (SONET).                                                                       |

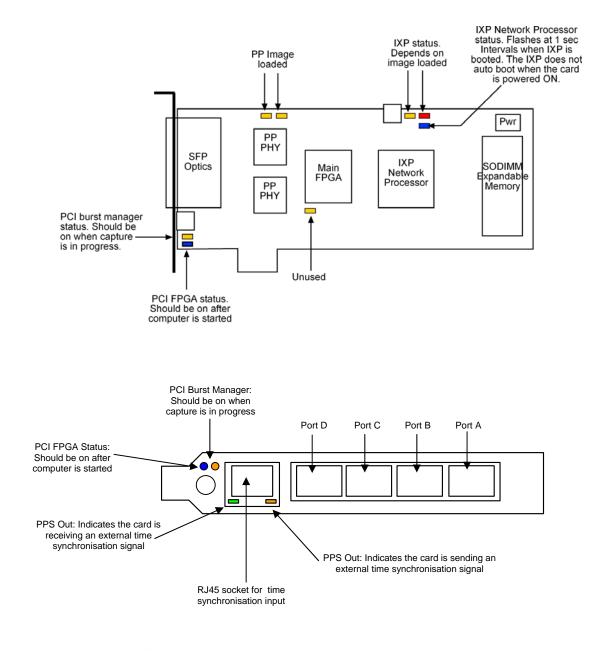

# LEDs and Inputs

Before you begin to configure the DAG card it is important to understand the function of the various LEDs associated with the card, as well as the sockets on the PCI bracket.

# Receiver Port Signal Levels

**Caution:** Ensure that you insert <u>only</u> OC-3/OC-12 modules. <u>Do not</u> use OC-48 or GiG-E modules as these will destroy the PHY FPGA

The card supports 1310 nanometer singlemode and multimode fibre attachments with optical signal strength between 0 dBm and -22 dBm.

If there is doubt, check card receiver ports light levels are correct using an optical power meter.

The card receiver ports are the lower of each dual-LC-style connectors, the closest to the PCI-Express slot.

Cover card transmit ports with LC-style plugs to prevent dust and mechanical hazards damaging optics if not in use.

**Note:** If you remove the optics modules for any reason they will not automatically power on when re-inserted. You will need to turn them on using the sfppwr option when you configure the card channelised or concatenated operation.

Specific Network Configuration

For detailed information on configuring the DAG 7.1S for data capture on concatenated and channelised networks please refer to <u>Chapter 4:</u> <u>Concatenated Configuration</u> and <u>Chapter 5: Channelised Configuration</u>.

EDM 01-17 DAG 7.1S Card User Guide

# Chapter 4: Concatenated Configuration

Load the FPGA Images **Note**: Before you can configure the card for capture you must first load the card with the appropriate FPGA images for the type of data you want to capture. It is important you understand the protocol used by the network to which you want to connect. If you do not load the correct image for the protocol you will not be able to capture data.

• Place the card in "eql" mode to prevent any erroneous signals interfering with the images during loading using :

dagconf -d0 eql (where "0" is the device number of the DAG card)

- Load the concatenated PCI-Express FPGA image: dagrom -rvp -d0 -f xilinx/dag7lspci-conc-terf.bit

- Load the concatenated PHY FPGA image:

dagld -x -d0 xilinx/dag71spp-conc-terf.bit: xilinx/dag71spp-conc-terf.bit

# Available

Display

Current

Configuration

**Configurations** The available concatenated configurations are shown below:

| Number of<br>Ports | Line Type     | VC Type and<br>Number | Protocol |

|--------------------|---------------|-----------------------|----------|

| 4                  | OC-3c/STM-1c  | 4 x VC-4              | PoS/ATM  |

| 4                  | OC-12c/STM-4c | 4 x VC-4-4c           | PoS/ATM  |

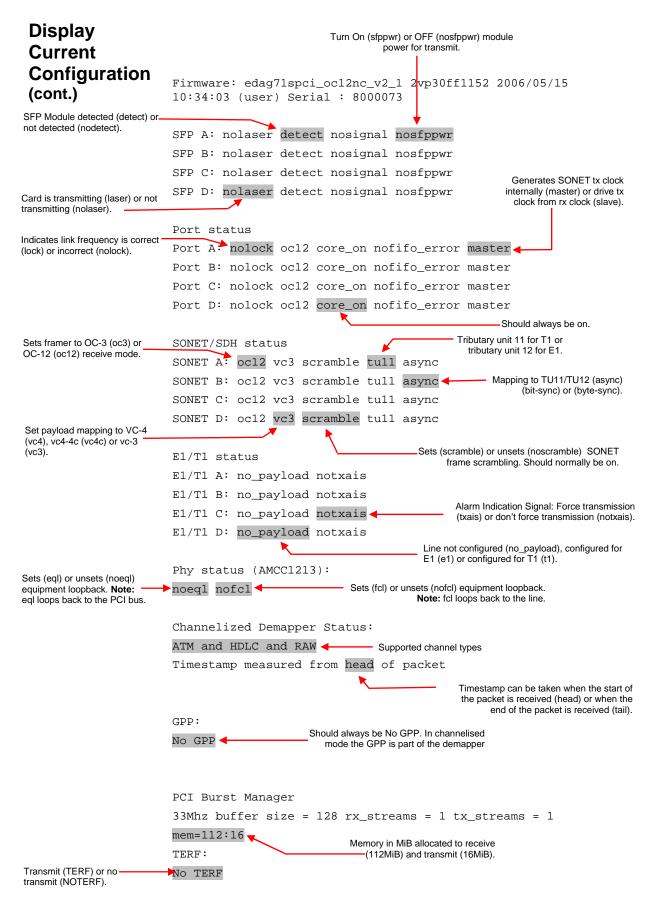

Once you have loaded the appropriate images you should run the dagconfig tool without arguments to display the current card configuration and verify the firmware has loaded correctly, using:

dagconfig -d0 (where "0" is the device number of the DAG card)

An explanation of the default dagconfig output is shown on the following page:

**Note:** The dagconfig default output may include some information that is not applicable to concatenated networks and these are indicated in the example

| Display                                                                  | Turns ON (sfppwr) or OFF (nosfppwr)<br>module power for transmit                                                                                       |  |  |  |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Current<br>Configuration                                                 | Firmware: edag71spci_oc12c_v2_1 2vp30ff1152 2006/02/21 08:53:53<br>(user) Serial : 8000073                                                             |  |  |  |

| (cont.)                                                                  | Generate SONET tx clock                                                                                                                                |  |  |  |

|                                                                          | clock from rx clock (slave).                                                                                                                           |  |  |  |

|                                                                          | SFP B: nolaser detect nosignal nosfppwr                                                                                                                |  |  |  |

|                                                                          | SFP C: nolaser detect nosignal nosfppwr<br>SFP D: nolaser detect nosignal nosfppwr disables (enable) or<br>disables (disable) Port A,                  |  |  |  |

| Card is enabled for transmission                                         | SFP D: nolaser detect nosignal nosfppwr disables (disable) Port A,<br>B, C or D for capture.                                                           |  |  |  |

| (laser) or not enabled (nolaser)                                         | Port status                                                                                                                                            |  |  |  |

| Indicates link frequency is correct                                      | Port A: nolock oc12 core_on nofifo_error master enablea                                                                                                |  |  |  |

| (lock) or incorrect (nolock).                                            | Port B: nolock oc12 core_on nofifo_error master enableb                                                                                                |  |  |  |

|                                                                          | Port C: nolock ocl2 core_on nofifo_error master enablec                                                                                                |  |  |  |

|                                                                          | Port D: nolock oc12 <pre>core_on</pre> nofifo_error master enabled                                                                                     |  |  |  |

|                                                                          | <b>↑</b>                                                                                                                                               |  |  |  |

| Sets framer to OC-3 (oc3) or                                             | SONET/SDH status Should always be on.                                                                                                                  |  |  |  |

| OC-12 (oc12) receive mode.                                               | SONET A: ocl2 vc3 scramble tull async                                                                                                                  |  |  |  |

|                                                                          | SONET B: ocl2 vc3 scramble tull async                                                                                                                  |  |  |  |

|                                                                          | SONET C: oc12 vc3 scramble tull async concatenated networks.                                                                                           |  |  |  |

| Sets payload mapping to vc4 (vc4), vc4-4c (vc4) or                       | SONET D: oc12 vc3 scramble tull async                                                                                                                  |  |  |  |

| vc3 (vc3 not applicable to concatenated).                                | Sets (scramble) or unsets (noscramble) SONET<br>frame scrambling. Should normally be on.                                                               |  |  |  |

| concatenateu).                                                           | EI/II Status                                                                                                                                           |  |  |  |

|                                                                          | E1/T1 A: no_payload notxais<br>E1/T1 B: no_payload notxais Not applicable to                                                                           |  |  |  |

|                                                                          | E1/T1 C: no_payload notxais                                                                                                                            |  |  |  |

|                                                                          | E1/T1 D: no_payload notxais                                                                                                                            |  |  |  |

|                                                                          |                                                                                                                                                        |  |  |  |

| Sets (eql) or unsets (noeql)                                             | Phy status (AMCC1213):                                                                                                                                 |  |  |  |

| equipment loopback. <b>Note:</b> eql loops back to the PCI bus.          | Sets (fcl) or unsets (nofcl) facility         noeql nofcl         Ioopback. Note: fcl loops back to the line.                                          |  |  |  |

|                                                                          |                                                                                                                                                        |  |  |  |

|                                                                          | Concatenated Demapper Status:                                                                                                                          |  |  |  |

|                                                                          | pscramble crc32 atm noaidle Pass (aidle) or don't pass (noaidle) received idle cells. ATM only.                                                        |  |  |  |

|                                                                          | pscramble crc32 atm noaidle                                                                                                                            |  |  |  |

| Sets (pscramble) or                                                      | pscramble crc32 atm noaidle                                                                                                                            |  |  |  |

| unsets (nopscramble)                                                     | pscramble crc32 atm noaidle<br>Sets concatenated mapper/demapper to ATM cell                                                                           |  |  |  |

| Should normally be on.                                                   | receive mode (atm) or Packet over SONET mode (pos).                                                                                                    |  |  |  |

|                                                                          | Concatenated Mapper Status:<br>pscramble crc16 atm                                                                                                     |  |  |  |

|                                                                          | pscramble crc16 atm                                                                                                                                    |  |  |  |

|                                                                          | pscramble crc16 atm Enables PoS CRC16 checks (crc16), CRC32 checks (crc32) or disables PoS CRC checking (nocrc).                                       |  |  |  |

|                                                                          | pscramble crc16 atm                                                                                                                                    |  |  |  |

|                                                                          |                                                                                                                                                        |  |  |  |

| Default slen value. Only<br>first 48 bytes of packet will<br>be captured | GPP:       Indicates records will be generated with 64-bit         varlen slen=48 align64       alignment (align64). This is the only supported option |  |  |  |

|                                                                          | PCI Burst Manager                                                                                                                                      |  |  |  |

| Transmit (TERF) or no                                                    | 33Mhz buffer size = 128 rx_streams = 1 tx_streams = 1                                                                                                  |  |  |  |

| transmit (NO TERF).                                                      | mem=112:16                                                                                                                                             |  |  |  |

|                                                                          | TERF: Memory in MiB allocated to receive (112MiB) and transmit (16MiB) streams.                                                                        |  |  |  |

| <b>,</b>                                                                 | No TERF                                                                                                                                                |  |  |  |

|                                                                          |                                                                                                                                                        |  |  |  |

| Display<br>Current<br>Configuration<br>(cont.) | If the firmware has not loaded correctly the dagconfig output will indicate<br>"component not found" as the SONET/SDH status and El/T1 status as<br>shown below:<br>SONET/SDH status<br>SONET A: component not found.<br>SONET B: component not found.<br>SONET C: component not found.<br>SONET D: component not found.<br>El/T1 status<br>El/T1 A: component not found.<br>El/T1 B: component not found.<br>El/T1 C: component not found.<br>El/T1 D: component not found.                        |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                | <ul> <li>In this case you should perform the following steps:</li> <li>Check the firmware image that you are using and ensure that it is correct for your network configuration and protocol,</li> <li>Then reload the firmware as described in <i>Load the FPGA Images</i> earlier in this chapter.</li> <li>If after performing these steps dagconfig still displays "component not found" please contact Endace Customer Support at <u>support@endace.com</u> for further assistance.</li> </ul> |

| Verify Optical<br>Signal                       | As shown on the previous page, the dagconfig output displays whether or<br>not a port is receiving a valid optical signal.<br>SFP A: laser detect signal nosfppwr<br>SFP B: laser detect nosignal nosfppwr<br>No valid signal received<br>To receive a valid optical signal, both ends of the link must use be using the<br>same type of optical transceivers. In addition the optical fiber used must<br>match the requirements of the optical transceiver and be in good condition.               |

# Verify Mapping/ Framing Setup

#### Parameters

As shown on the previous page, the dagconfig output displays whether or not mapping and framing is setup correctly.

For correct setup both ends of the link must match the framing and mapping parameters. The main parameters involved in setting the framing are:

- Link speed (oc3/oc12)

- Clock master (master/slave)

- Payload mapping (vc4c/vc4)

|                          | Port status                                                                    |  |  |  |

|--------------------------|--------------------------------------------------------------------------------|--|--|--|

|                          | Port A: lock oc12 core_on nofifo_error slave                                   |  |  |  |

|                          | Port B: nolock ocl2 core_on nofifo_error slave                                 |  |  |  |

| Link not setup correctly |                                                                                |  |  |  |

|                          | SONET/SDH status                                                               |  |  |  |

|                          | SONET A: oc12 vc4c scramble tu11 async                                         |  |  |  |

|                          | SONET B: ocl2 vc4c scramble tull async Not applicable to concatenated networks |  |  |  |

SONET C: oc12 vc4c scramble tu11 async SONET D: oc12 vc4c scramble tu11 async

**Different Port Configurations** The DAG card allows different ports to have different configurations. For

example if you want to configure only Ports A and B for OC-3c VC-4c you could do so using the following command:

```

dagconfig -d0 default -1 -4 oc3 vc4

Port status

Port A: nolock oc3 core_on nofifo_error master enablea

Port B: nolock oc12 core_on nofifo_error master enablec

Port C: nolock oc12 core_on nofifo_error master enablec

SONET/SDH status

SONET A: oc3 vc4 scramble tull async

SONET B: oc3 vc4 scramble tull async

SONET C: oc12 vc4 scramble tull async

SONET D: oc12 vc4 scramble tull async

```

#### **ATM Mode**

When configuring the DAG card for ATM mode ensure you configure it to match the characteristics of the network you wish to monitor.

Please refer to **Display Current Configuration** earlier in this chapter for a full explanation of dagconfig outputs.

Note: The order in which the configuration options appear in the command line is important. Therefore you should use default and reset before other options in the command line.

The example below has been configured for OC-12c VC-4-4c on ports A and B with ports C and D unused:

| dagconfig                  | -d0 reset default                          | atm oc12 vc         | 4c sfppwr                  |                                                                            |

|----------------------------|--------------------------------------------|---------------------|----------------------------|----------------------------------------------------------------------------|

| Note position command line |                                            | VC-4-4c             |                            | Turns the optics modules<br>on if they have previously<br>been turned off. |

|                            | nware: edag71spci_c<br>5/02/21 08:53:53 (u |                     |                            | 1152                                                                       |

| SFP                        | A: nolaser detect                          | signal sfpp         | wr                         |                                                                            |

| SFP                        | B: nolaser detect                          | signal sfpp         | wr                         |                                                                            |

| SFP                        | C: nolaser detect                          | nosignal sf         | ppwr                       |                                                                            |

| SFP                        | D: nolaser detect                          | nosignal sf         | ppwr                       |                                                                            |

| Port                       | t status                                   | k setup correctly   |                            |                                                                            |

| Port                       | t A: lock oc12 core                        | _on nofifo_         | error maste                | r enablea                                                                  |

| Port                       | t B: lock oc12 core                        | e_on nofifo_        | error maste                | r enableb                                                                  |

| Port                       | t C: nolock ocl2 co                        | ore_on nofif        | o_error mas                | ter enablec                                                                |

| Port                       | t D: nolock oc12 cc                        | ore_on nofif        | o_error mas                | ter enabled                                                                |

| SONI                       | Li<br>ET/SDH status                        | nk not setup correc | tly                        |                                                                            |

| SON                        | ET A: ocl2 vc4c scr                        | amble tull          | async                      |                                                                            |

| SON                        | ET B: ocl2 vc4c scr                        | amble tull          | async                      | Not applicable to<br>oncatenated networks                                  |

| SON                        | ET C: ocl2 vc4c scr                        | amble tull          |                            |                                                                            |

| SON                        | ET D: ocl2 vc4c scr                        | amble tull          | async                      |                                                                            |

| E1/5                       | Il status                                  |                     |                            |                                                                            |

| E1/1                       | F1 A: no_payload nc                        | otxais              | Neteral                    |                                                                            |

| E1/1                       | <pre>F1 B: no_payload nc</pre>             | txais ┥ 🗕           | Not appl<br>concatenated r |                                                                            |

| E1/1                       | F1 C: no_payload no                        | otxais              |                            |                                                                            |

| E1/1                       | T1 D: no_payload no                        | otxais              |                            |                                                                            |

| Phy                        | status (AMCC1213):                         |                     |                            |                                                                            |

| noed                       | ql nofcl                                   |                     |                            |                                                                            |

| Cond                       | catenated Demapper                         | Status: Not         | applicable to ATM          |                                                                            |

| psci                       | ramble crc32 atm nc                        |                     |                            |                                                                            |

| psci                       | ramble crc32 atm nc                        | aidle               |                            |                                                                            |

| psci                       | ramble crc32 atm nc                        | aidle               |                            |                                                                            |

| psci                       | ramble crc32 atm no                        | aidle               |                            |                                                                            |

| ATM Mode | Concatenated Mapper Status:                           |

|----------|-------------------------------------------------------|

| (cont.)  | pscramble crc16 atm                                   |

| (••••••) | pscramble crc16 atm                                   |

|          | pscramble crc16 atm                                   |

|          | pscramble crc16 atm                                   |

|          | Not applicable to ATM                                 |

|          | GPP:                                                  |

|          | varlen slen=48 align64                                |

|          | PCI Burst Manager                                     |

|          | 33Mhz buffer size = 128 rx_streams = 1 tx_streams = 1 |

|          | mem=112:16                                            |

|          | TERF:                                                 |

|          | No TERF                                               |

### **PoS Mode**

To configure the DAG card for PoS mode you must replace oc12 and vc4c to match your network configuration as shown below:

Please refer to <u>*Display Current Configuration*</u> earlier in this chapter for a full explanation of dagconfig outputs.

```

dagconfig -d0 reset default pos oc12 vc4c sfppwr slen=2048

VC-4-4c

Note position in

command line.

Recommended slen

value for PoS networks

Turns the optics modules on if they have

previously been turned off.

Firmware: edag71spci_oc12c_pci_v2_23 2vp30ff1152

2006/02/21 08:53:53 (user) Serial : 8000073

SFP A: nolaser detect signal sfppwr

SFP B: nolaser detect signal sfppwr

SFP C: nolaser detect nosignal sfppwr

SFP D: nolaser detect nosignal sfppwr

Port status

Port A: lock oc12 core_on nofifo_error master enablea

Port B: lock oc12 core_on nofifo_error master enableb

Port C: nolock ocl2 core on nofifo error master enablec

Port D: nolock oc12 core_on nofifo_error master enabled

SONET/SDH status

SONET A: oc12 vc4c scramble tu11 async

SONET B: ocl2 vc4c scramble tull async

Not applicable to PoS

SONET C: oc12 vc4c scramble tu11 async

SONET D: oc12 vc4c scramble tu11 async

```

| PoS Mode                |                                                                                                                                                                 |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (cont.)                 | E1/T1 status                                                                                                                                                    |

| (00111)                 | El/T1 A: no_payload notxais                                                                                                                                     |

|                         | E1/T1 B: no_payload notxais Not applicable to concatenated networks                                                                                             |

|                         | E1/T1 C: no_payload notxais                                                                                                                                     |

|                         | E1/T1 D: no_payload notxais                                                                                                                                     |

|                         | Phy status (AMCC1213):                                                                                                                                          |

|                         | noeql nofcl                                                                                                                                                     |

|                         | Concatenated Demapper Status:                                                                                                                                   |

|                         | pscramble crc32 pos noaidle                                                                                                                                     |

|                         | Concatenated Mapper Status:                                                                                                                                     |

|                         | pscramble crc16 pos                                                                                                                                             |

|                         | GPP:                                                                                                                                                            |

|                         | varlen slen=2048 align64                                                                                                                                        |

|                         | PCI Burst Manager                                                                                                                                               |

|                         | 33Mhz buffer size = 128 rx_streams = 1 tx_streams = 1                                                                                                           |

|                         | mem=112:16                                                                                                                                                      |

|                         | TERF:                                                                                                                                                           |

|                         | No TERF                                                                                                                                                         |

|                         |                                                                                                                                                                 |

| Interface<br>Statistics | When you have configured the card according to your specific requirements you can view the interface statistics to check the status of each of the links using: |

|                         | dagconfig −d0 −si ← Display statistics once (-s)<br>or at 1 sec intervals (-si)                                                                                 |

|                         | Example outputs are shown below:                                                                                                                                |

**Note:** "1" indicates the condition is present on the link "0" indicates the condition is not present on the link. See *Status Conditions* later in this chapter for a full description of each of the status conditions.

### PoS OC12 Stream

Interface Statistics (cont.)

# In the example below the card is locked to a PoS OC-12 stream on ports A and

In the example below the card is set to OC-3 PoS while the line carries OC-12 PoS:

| Line Interface Unit (LIU) conditions |         |              |     |     |    |    |    |     |    |     |

|--------------------------------------|---------|--------------|-----|-----|----|----|----|-----|----|-----|

|                                      | Pointer | r conditions |     |     |    |    |    |     |    |     |

| Port                                 | VC      | LOS          | LOF | OOF | в1 | в2 | в3 | REI | C2 | PTR |

| A:                                   | 0       | 1            | 1   | 1   | 0  | 0  | 0  | 0   | 6d | lop |

| в:                                   | 0       | 1            | 1   | 1   | 0  | 0  | 0  | 0   | fd | lop |

|                                      |         |              |     |     |    |    |    |     |    |     |

| Port                                 | VC      | LOS          | LOF | OOF | B1 | В2 | В3 | REI | C2 | PTR |

| A:                                   | 0       | 1            | 1   | 1   | 0  | 0  | 0  | 0   | 44 | lop |

| B:                                   | 0       | 1            | 1   | 1   | 0  | 0  | 0  | 0   | 23 | lop |

|                                      |         |              |     |     |    |    |    |     |    |     |

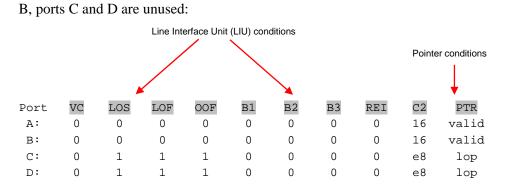

## **ATM Cell Stream**

In the example below the card is locked to an ATM OC-12 stream on ports A and B, ports C and D are unused:

|      | Point | er conditions |     |     |    |    |    |     |    |       |

|------|-------|---------------|-----|-----|----|----|----|-----|----|-------|

|      |       |               |     |     |    |    |    |     |    | ↓ I   |

| Port | VC    | LOS           | LOF | OOF | в1 | в2 | в3 | REI | C2 | PTR   |

| A:   | 0     | 0             | 0   | 0   | 0  | 0  | 0  | 0   | 13 | valid |

| B:   | 0     | 0             | 0   | 0   | 0  | 0  | 0  | 0   | 13 | valid |

| C:   | 0     | 1             | 1   | 1   | 0  | 0  | 0  | 0   | 4b | lop   |

| D:   | 0     | 1             | 1   | 1   | 0  | 0  | 0  | 0   | e8 | lop   |

### Interface Status Conditions

Statistics (cont.) A definition of each of the status conditions is described below:

| Condition  | Definition                                                                                                                                                                                                                |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B1, B2, B3 | Bit interleaved parity error as reported by SONET B1, B2<br>and B3 overhead octets. Indicates the connection between the<br>card and the network is impaired.                                                             |

|            | If OOF and LOF conditions are <u>also</u> set the OCx carrier configuration is incorrect.                                                                                                                                 |

|            | If OOF and LOF conditions are <u>not</u> set the there is a signal<br>problem related to low light levels reaching the optical<br>receivers, or there are true SONET-level errors on the<br>equipment operating the link. |

| C2         | Path signal label.<br>Reflects the content of SONET C2 overhead octet. Typical<br>settings are:<br>13ATM<br>16 PPP w/SPE scrambling<br>CF PPP wo/SPE scrambling                                                           |

|            | Changing values for this condition indicate a SONET level error.                                                                                                                                                          |

| LOF        | Loss of Frame.<br>Indicates Out of Frame (OOF) condition has been asserted for<br>more than 2 milliseconds.                                                                                                               |

| PTR        | Indicates if the pointer processing logic has locked to the SONET stream. Possible values are:                                                                                                                            |

|            | valid: The pointer has locked to the SONET stream.<br>lop (loss of pointer): The pointer has not locked to<br>the SONET stream and may indicate incorrect OC-<br>3/OC-12 setting.                                         |

|            | conc: The card is configured for channelised data but the network is concatenated.                                                                                                                                        |

| LOS        | Loss of Signal.<br>There is either no signal at the receiver or the optical signal<br>strength is too low for the card to recognize.                                                                                      |

| OOF        | Out of Frame.<br>The section overhead processor is not locked to the SONET<br>stream and may indicate incorrect OC-3/OC-12 setting.                                                                                       |

| REI        | Remote Error Indicator.                                                                                                                                                                                                   |

| VC         | Virtual container number. Should always be "0" for concatenated networks.                                                                                                                                                 |

### **ATM Network**

If the card is connected to an ATM network and you have loaded the correct firmware for the network configuration the following values apply:

- C2 should be "13"

- PTR should be "valid"

- Remaining statistics should be "0"

#### **PoS Network**

If the card is connected to an PoS network and you have loaded the correct firmware for the network configuration the following values apply:

- C2 should be "16" for PPP or "cf" for HDLC

- PTR should be "valid"

- Remaining statistics should be "0"

# Verify Configuration

You can verify the card configuration by checking settings and path label for any errors as follows:

- Ensure LOS is 0, otherwise check light levels.

- Ensure OOF and LOF are 0, otherwise change OC-3 settings to OC-12 or vice versa.

- Ensure PTR is valid

- Ensure no bit interleaved parity errors occur, otherwise check cabling and light levels.

- Ensure C2 is correct for the payload

- Ensure PoS scrambling and CRC settings are correct.

# **Chapter 5: Channelised Configuration**

Load the **FPGA** Images Note: Before you can configure the card for capture you must first load the card with the appropriate FPGA images for the type of data you want to capture. It is important you understand the protocol used by the network to which you want to connect. If you do not load the correct image for the protocol you will not be able to capture data.

Place the card in "eql" mode to prevent any erroneous signals interfering with the images during loading using

dagconf -d0 eql (where "0" is the device number of the DAG card)

- **PCI-Express FPGA image:** dagrom -rvp -d0 -f xilinx/dag71spci-chan-terf.bit

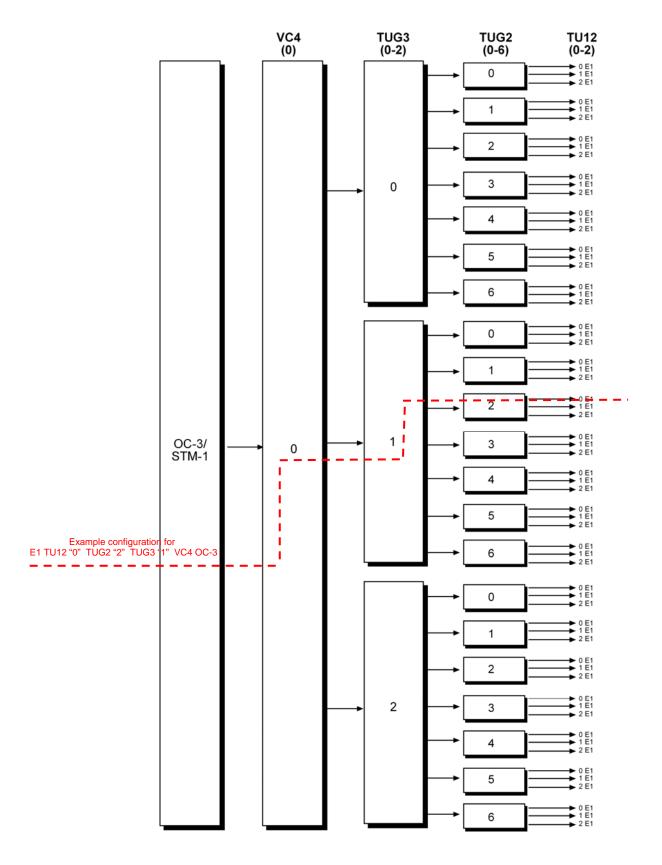

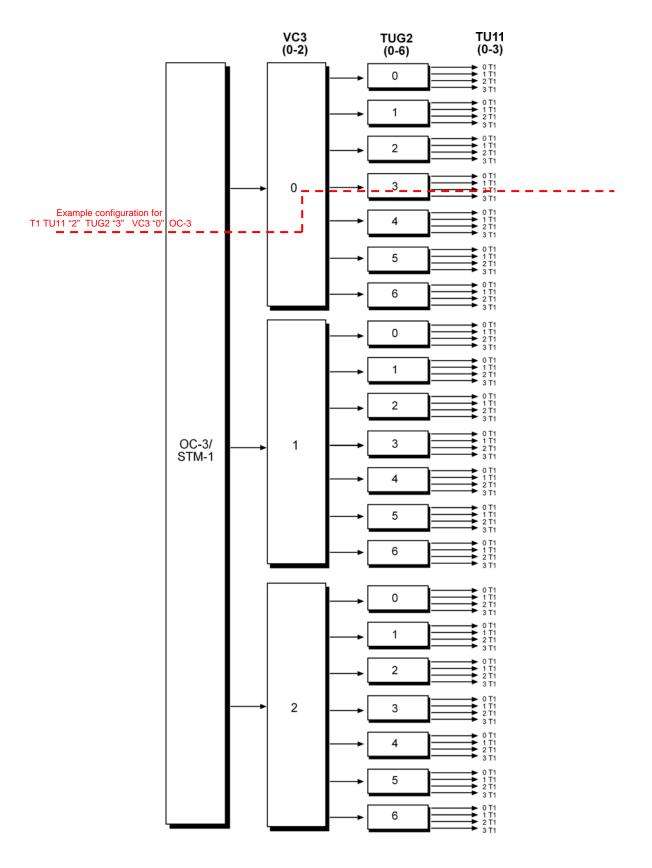

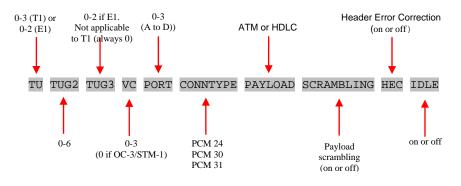

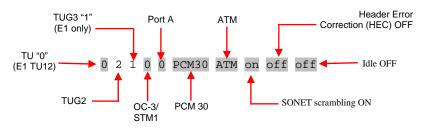

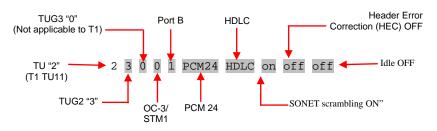

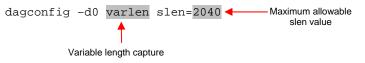

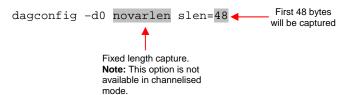

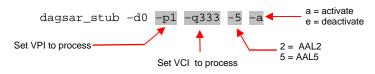

- PHY FPGA image: dagld -x -d0 xilinx/dag71spp-chan-terf.bit: xilinx/dag71spp-chan-terf.bit